Frequency set to 6MHz

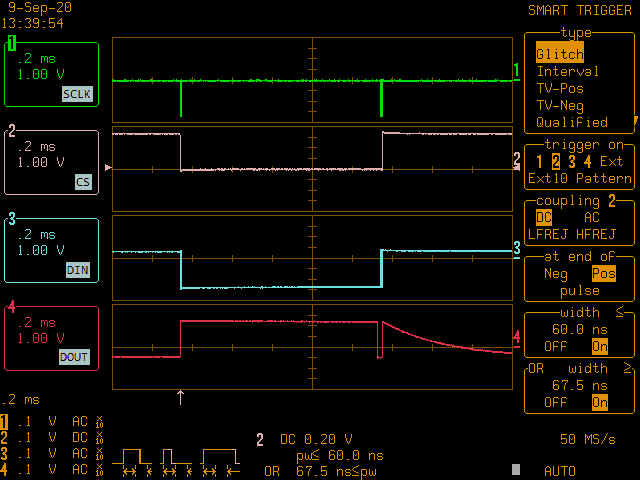

Two pikes was observed on the SCLK line, which correspond to the W/R commands of 4 and 5 bytes in particullar. The delay between these two block corresponds exactly to the 1msec delay in the code.

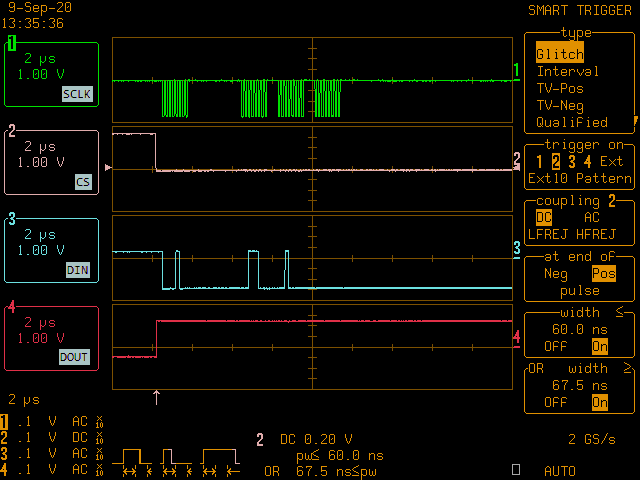

Sending of 4 bytes:

Please notice the longer delay on the SCLK line. It is unclear why the delay occures. The delay can be few tens of ns shorter or longer in time. The measured clock corresponds to the 6MHz set in the SPI parameters.

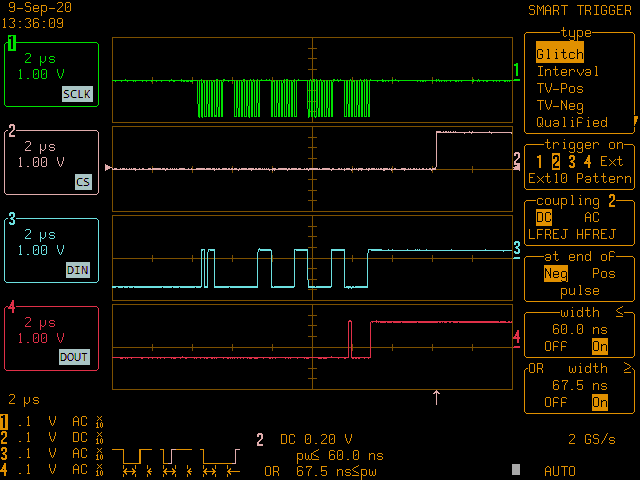

Sending of 5 bytes:

The clocking in the SCLK line occurs always regullary. Not any deviations was observed in this 5 bytes block.

According to the datasheet of the operation amplifier a delay of at least 1msec must be introduced after settings of parameters, which cause the wake up of the OpAmp. This wait state is required only for the Mode1.